# mos integrated circuit $\mu$ PD75328

# **4-BIT SINGLE-CHIP MICROCOMPUTER**

## DESCRIPTION

The  $\mu$ PD75328 is one of the 75X Series 4-bit single-chip microcomputer, and has a data processing capability comparable to that of an 8-bit microcomputer.

In addition to high-speed operation with 0.95  $\mu$ s minimum instruction execution time for the CPU, the  $\mu$ PD75328 can also process data in 1-, 4-, and 8-bit units. Therefore, as a 4-bit single-chip microcomputer chip having a built-in LCD controller/driver and A/D converter, its data processing capability is the highest in its class in the world.

The  $\mu$ PD75P328 with one-time PROM, which is replaced with the internal mask ROM for a  $\mu$ PD75328, is applicable for evaluating systems under development, or for small-scale production of developed systems.

"Detailed functions are described in the following user's manual. Be sure to read it for designing." " $\mu$ PD75328 User's Manual: IEM-5045"

### **FEATURES**

- Capable of high-speed operation and variable instruction execution time to power save

- 0.95  $\mu$ s, 1.91  $\mu$ s, 15.3  $\mu$ s (Main system clock: operating at 4.19 MHz)

- 122 μs (Subsystem clock: operating at 32.768 kHz)

- 75X architecture comparable to that for an 8-bit microcomputer is employed

- Built-in programmable LCD controller/driver

- Built-in 8-bit resolution A/D converter: 6 channels

- Clock operation at reduced power dissipation: 5  $\mu$ A TYP. (operating at 3 V)

- Timer function: 3 channels

- Interrupt functions especially enhanced for applications, such as remote control receiver

- Pull-up resistors can be provided for 35 I/O lines

- Built-in NEC standard serial bus interface (SBI)

#### **APPLICATIONS**

Cameras, blood pressure gauges, airconditioners, etc.

#### **ORDERING INFORMATION**

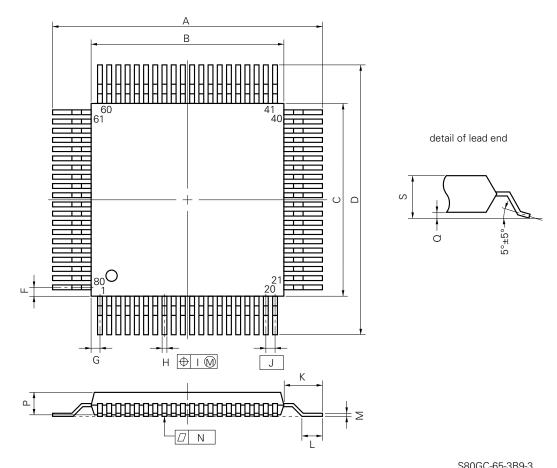

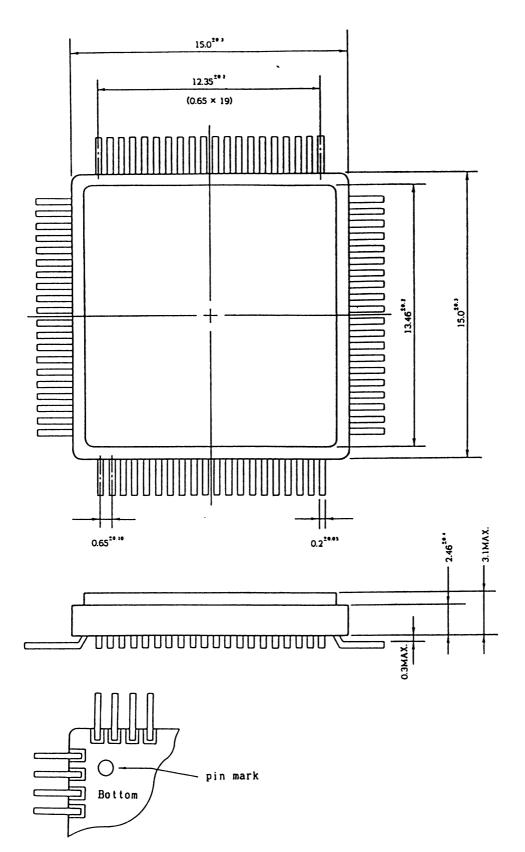

| Part Number        | Package                     | Quality Grade |  |

|--------------------|-----------------------------|---------------|--|

| μPD75328GC-xxx-3B9 | 80-pin plastic QFP (🗆 14mm) | Standard      |  |

Remarks: xxx is ROM code number.

Please refer to "Quality Grade on NEC Semiconductor Devices" (Document Number IEI-1209) published by NEC Corporation to know the specification of quality grade on the devices and its recommended applications.

The information in this document is subject to change without notice.

# FUNCTIONAL OUTLINE (1/2)

| ltem                                              | Item Function |                                                                                                                                                                                                                                            |                                                                                                                                                                     |                                                                                                              |                                                                                                     |  |

|---------------------------------------------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|--|

| Number of B<br>Instructions                       | asic          | 41                                                                                                                                                                                                                                         |                                                                                                                                                                     |                                                                                                              |                                                                                                     |  |

| Instruction<br>Execution Ti                       |               |                                                                                                                                                                                                                                            |                                                                                                                                                                     |                                                                                                              |                                                                                                     |  |

| Internal                                          | ROM           | 8064 ×                                                                                                                                                                                                                                     | 8-bit                                                                                                                                                               |                                                                                                              |                                                                                                     |  |

| Memory                                            | RAM           | 512 × 4                                                                                                                                                                                                                                    | -bit                                                                                                                                                                |                                                                                                              |                                                                                                     |  |

| General-Purp<br>Registers                         | ose           | 4-bit m                                                                                                                                                                                                                                    | anip                                                                                                                                                                | ulation: 8×4 banks, 8-bit manipula                                                                           | ation: 4×4 banks                                                                                    |  |

| I/O Line                                          | no nine \     |                                                                                                                                                                                                                                            | 8                                                                                                                                                                   | CMOS Input pins                                                                                              | Internal pull-up resistor<br>— specification by software                                            |  |

| which also                                        | serve         | 44                                                                                                                                                                                                                                         | 20                                                                                                                                                                  | CMOS input/output pins                                                                                       | is possible (except P00).                                                                           |  |

| as LCD driv<br>Excluding t                        |               |                                                                                                                                                                                                                                            | 8                                                                                                                                                                   | CMOS output pins                                                                                             | Also serve as segment pins                                                                          |  |

| pins which<br>specifically<br>vided for d<br>LCD. | is<br>pro-    |                                                                                                                                                                                                                                            | 8                                                                                                                                                                   | N-ch open-drain<br>input/output                                                                              | Withstand voltage: 10V<br>Internal pull-up resistor<br>specification by mask option<br>is possible. |  |

| LCD Controll<br>Driver                            | er/           | <ul> <li>LCD drive output pins</li> <li>Segment output pins: 20 (CMOS output pins: 8)</li> <li>Common output pins: 4</li> <li>Capable of driving up to 20 × 4 segments</li> <li>Display output mode: Static, 1/2, 1/3, 1/4 duty</li> </ul> |                                                                                                                                                                     |                                                                                                              |                                                                                                     |  |

| A/D Converte                                      | er            | •                                                                                                                                                                                                                                          | Oper                                                                                                                                                                | tion x 6 channels (successive app<br>ating voltage VDD = 3.5 to 6.0 V<br>conversion speed 40.1 µs (operation |                                                                                                     |  |

| Timer<br>MHz)                                     |               | 3 chs                                                                                                                                                                                                                                      | Can be used as watchdog timer      Clock timer      0.5 second interval generation                                                                                  |                                                                                                              | r                                                                                                   |  |

|                                                   |               |                                                                                                                                                                                                                                            | <ul> <li>Count clock source slectable (4.19 MHz/32.768 kHz)</li> <li>Clock advance mode (3.9 ms time interval generation)</li> <li>Buzzer output (2 kHz)</li> </ul> |                                                                                                              |                                                                                                     |  |

| Serial<br>Interface                               |               | Clock synchronized serial interface<br>• Internal NEC standard serial bus interface (SBI mode)<br>• 3-line serial I/O mode MSB/LSB first selectable<br>• 2-line serial I/O mode                                                            |                                                                                                                                                                     |                                                                                                              |                                                                                                     |  |

| Bit Sequentia<br>Buffer                           | al            | Special bit manipulation memory: 16 bits                                                                                                                                                                                                   |                                                                                                                                                                     |                                                                                                              |                                                                                                     |  |

| Clock Output<br>(PCL)                             |               | Φ, 524, 262, 65.5 kHz (Main system clock: 4.19 MHz)                                                                                                                                                                                        |                                                                                                                                                                     |                                                                                                              |                                                                                                     |  |

| Buzzer Outpu<br>(BUZ)                             | ıt            | 2 kHz (with main system clock or subsystem clock operated)                                                                                                                                                                                 |                                                                                                                                                                     |                                                                                                              |                                                                                                     |  |

| Vector Interr                                     | upt           | External: 3     Internal: 3                                                                                                                                                                                                                |                                                                                                                                                                     |                                                                                                              |                                                                                                     |  |

| Test Input                                        |               |                                                                                                                                                                                                                                            | External: 1     Internal: 1                                                                                                                                         |                                                                                                              |                                                                                                     |  |

# FUNCTIONAL OUTLINE (2/2)

| ltem                           | Function                                                                                                                                                    |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| System Clock<br>Generator      | <ul> <li>Main system clock generation ceramic/crystal oscillator; 4.194304 MHz</li> <li>Subsystem clock generation crysal oscillator: 32.768 kHz</li> </ul> |

| Standby                        | STOP/HALT mode                                                                                                                                              |

| Operating<br>Temperature Range | -40 to +85°C                                                                                                                                                |

| Operating Supply<br>Voltage    | $V_{DD} = 2.7 \text{ to } 6.0 \text{ V}$                                                                                                                    |

| Package                        | 80-pin plastic QFP (□14 mm)                                                                                                                                 |

# CONTENTS

| 1.  | PIN  | CONFIGURATION (TOP VIEW)                      | 6          |

|-----|------|-----------------------------------------------|------------|

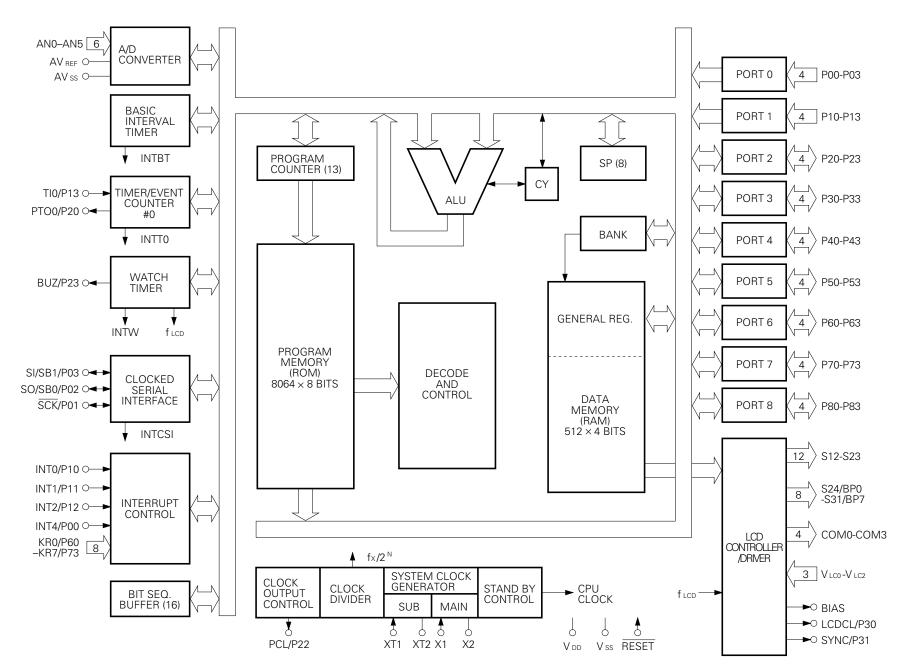

| 2.  | BLO  | CK DIAGRAM                                    | .7         |

| 3.  | PIN  | FUNCTIONS                                     | .8         |

|     | 3.1  | PORT PINS                                     | . 8        |

|     | 3.2  | NON PORT PINS                                 | 10         |

|     | 3.3  | PIN INPUT/OUTPUT CIRCUITS 1                   | 12         |

|     | 3.4  | RECOMMENDED PROCESSING OF UNUSED PINS 1       | 14         |

|     | 3.5  | SELECTION OF MASK OPTION 1                    | 15         |

|     | 3.6  | NOTES ON USING THE P00/INT4, AND RESET PINS 1 | 15         |

| 4.  | MEN  | IORY CONFIGURATION 1                          | 6          |

| 5.  | PER  | PHERAL HARDWARE FUNCTIONS 1                   | 8          |

|     | 5.1  | PORTS 1                                       | 18         |

|     | 5.2  | CLOCK GENERATOR CIRCUIT 1                     | 19         |

|     | 5.3  | CLOCK OUTPUT CIRCUIT                          | 20         |

|     | 5.4  | BASIC INTERVAL TIMER                          | 21         |

|     | 5.5  | WATCH TIMER                                   | 22         |

|     | 5.6  | TIMER/EVENT COUNTER                           | 22         |

|     | 5.7  | SERIAL INTERFACE                              | 24         |

|     | 5.8  | LCD CONTROLLER/DRIVER                         | 26         |

|     | 5.9  | A/D CONVERTER                                 | 28         |

|     | 5.10 | BIT SEQUENTIAL BUFFER 16 BITS 2               | 29         |

| 6.  | INTE | RUPT FUNCTIONS                                | 29         |

| 7.  | STAN | IDBY FUNCTIONS                                | ;1         |

| 8.  | RESE | T FUNCTION                                    | :2         |

| 9.  | INST | RUCTION SET                                   | ;4         |

| 10. | ELE  | CTRICAL SPECIFICATIONS                        | 10         |

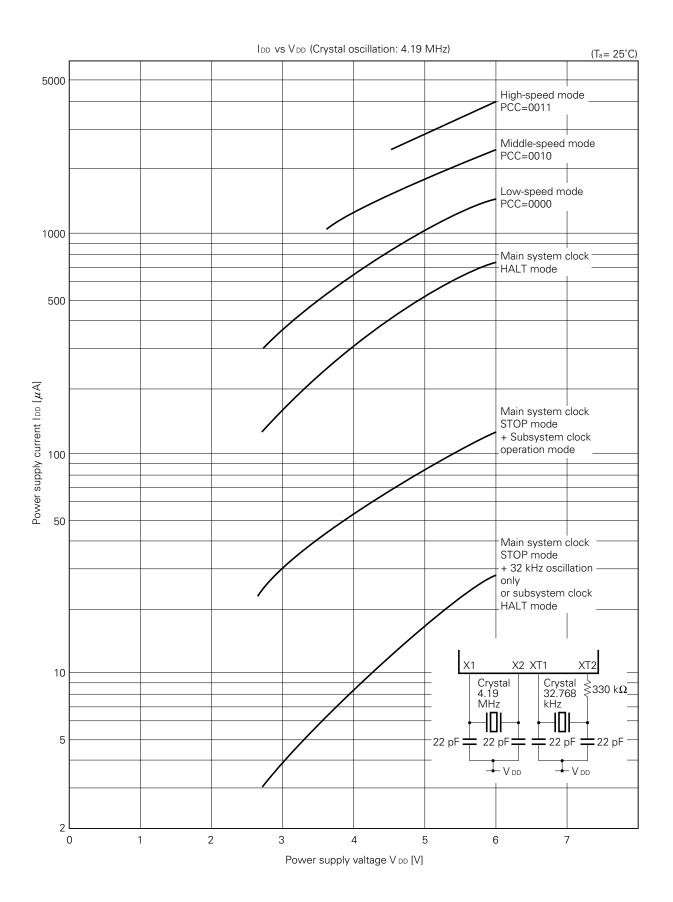

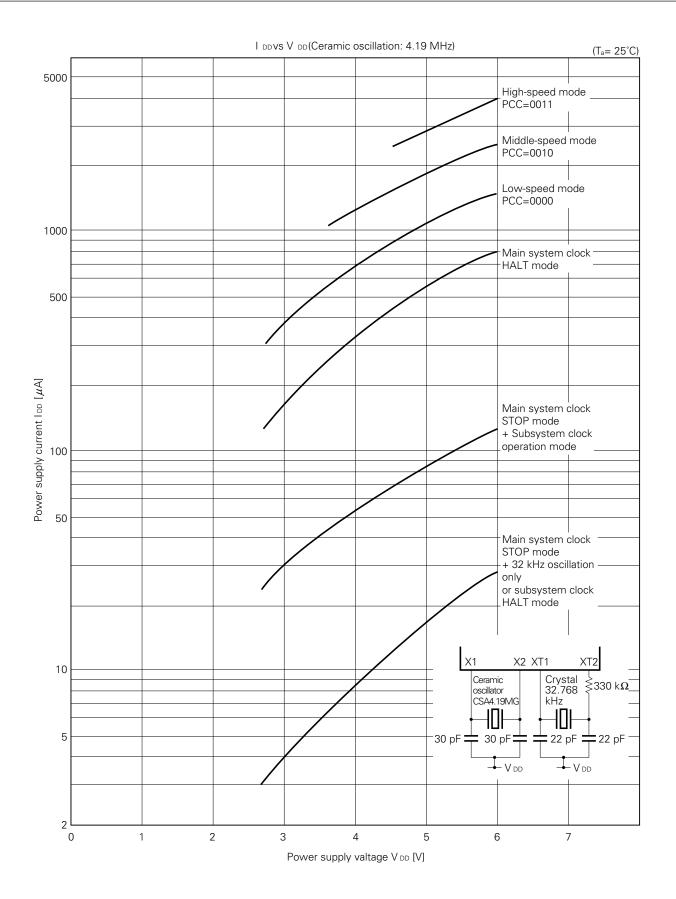

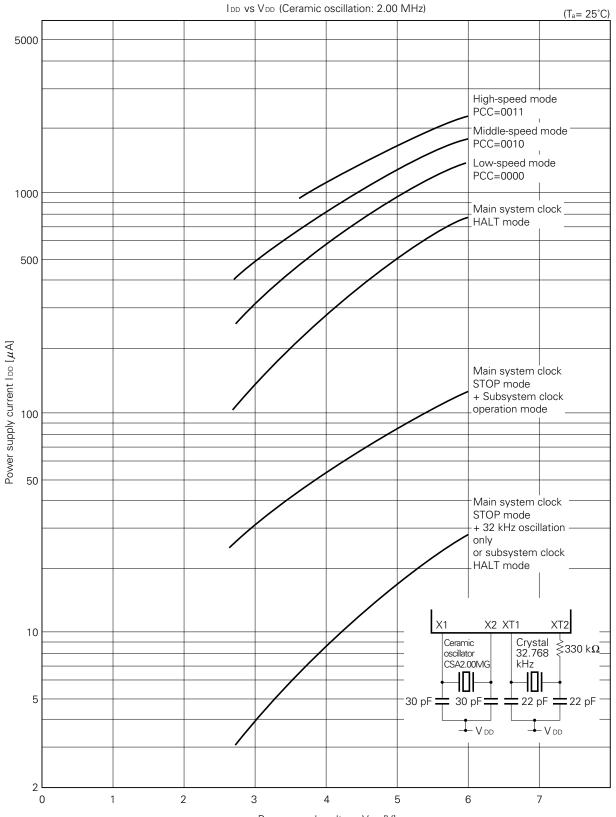

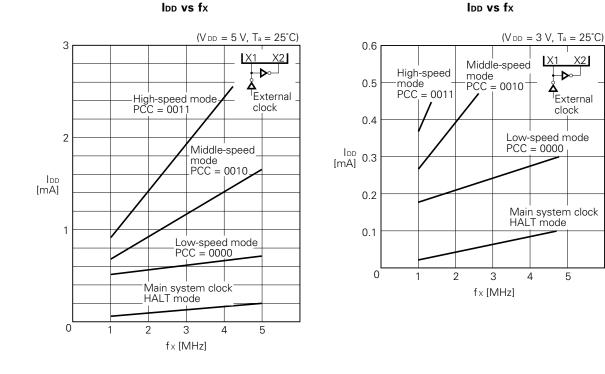

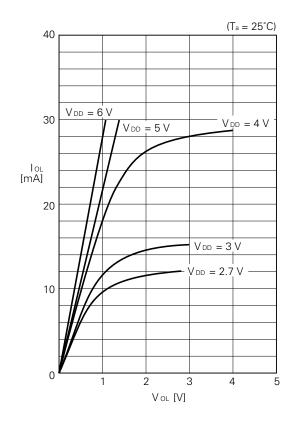

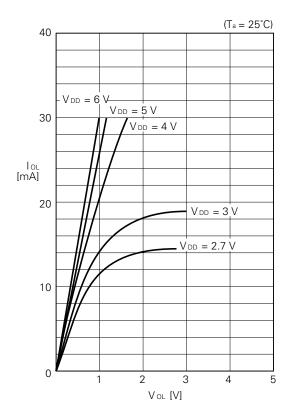

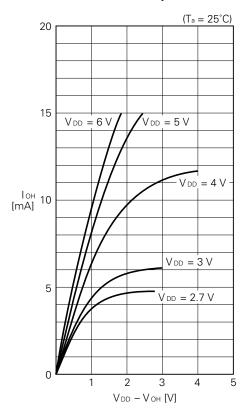

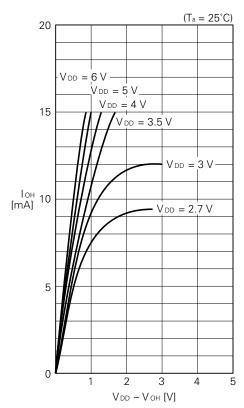

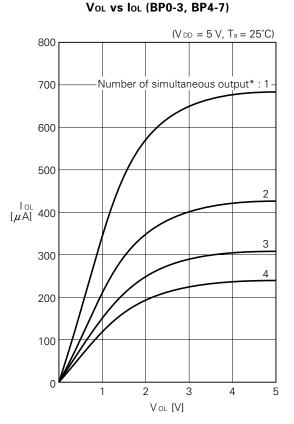

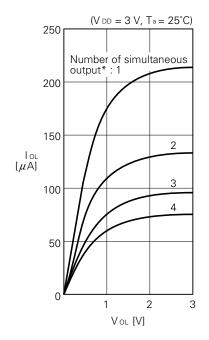

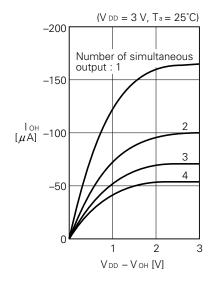

| 11. | СНА  | RACTERISTIC CURVES (REFERENCE VALUE)5         | <b>i</b> 3 |

| 12. | PAC  | KAGE DRAWINGS                                 | <b>9</b>   |

| 13. | REC  | OMMENDED SOLDERING CONDITIONS                 | 51         |

| APPENDIX A. | COMPARISON OF FEATURES BETWEEN µPD75328 AND µPD75308 | 62 |

|-------------|------------------------------------------------------|----|

| APPENDIX B. | DEVELOPMENT TOOLS                                    | 63 |

| APPENDIX C. | RELATED DOCUMENTS                                    | 64 |

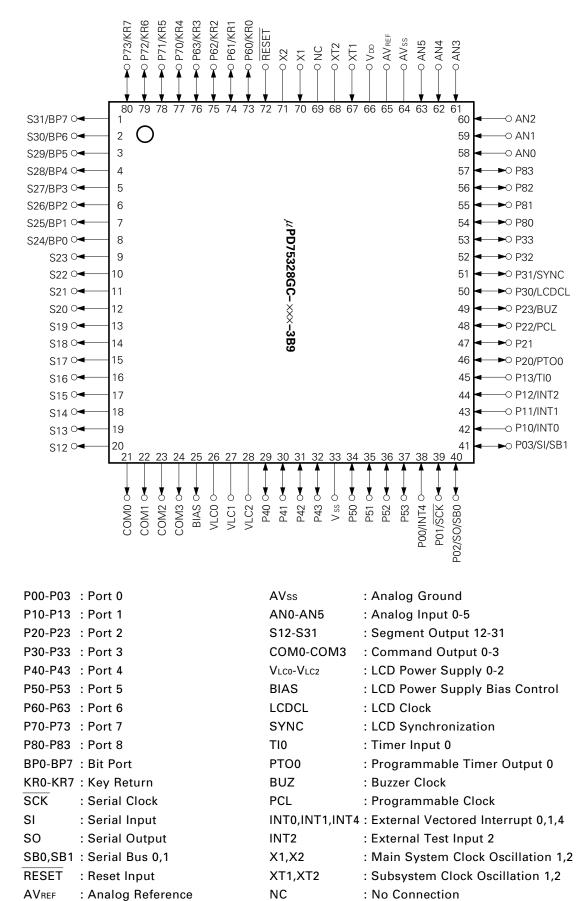

## 1. PIN CONFIGURATION (Top View)

# 3. PIN FUNCTIONS

#### 3.1 PORT PINS (1/2)

| Pin Name | Input/Output     | Also Served<br>As | Function                                                                                                                                                                                  | 8-Bit I/O | When Reset                                                                     | Input/<br>Output<br>Circuit<br>TYPE* <sup>1</sup> |

|----------|------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--------------------------------------------------------------------------------|---------------------------------------------------|

| P00      | Input            | INT4              |                                                                                                                                                                                           |           | Input -                                                                        | B                                                 |

| P01      | Input/<br>Output | SCK               | 4-bit input port (PORT0)<br>Pull-up resistors can be specified in 3-bit                                                                                                                   |           |                                                                                | F-A                                               |

| P02      | Input/<br>Output | SO/SB0            | units for the P01 to P03 pins by software.                                                                                                                                                | х         |                                                                                | (F)-B                                             |

| P03      | Input/<br>Output | SO/SB1            |                                                                                                                                                                                           |           |                                                                                | M-C                                               |

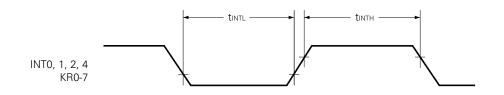

| P10      |                  | INT0              | With noise elimination function                                                                                                                                                           |           |                                                                                |                                                   |

| P11      | Input            | INT1              | 4-bit input port (PORT1)                                                                                                                                                                  | x         | Input                                                                          |                                                   |

| P12      | input            | INT2              | Internal pull-up resistors can be specified in 4-bit units by software.                                                                                                                   |           |                                                                                | B-C                                               |

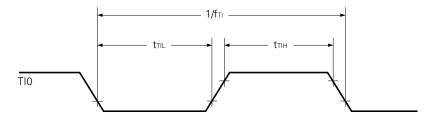

| P13      |                  | TI0               |                                                                                                                                                                                           |           |                                                                                |                                                   |

| P20      |                  | PTO0              |                                                                                                                                                                                           | v         | Input                                                                          | E-B                                               |

| P21      | Input/           | _                 | 4-bit input/output port (PORT2)<br>Internal pull-up resistors can be                                                                                                                      |           |                                                                                |                                                   |

| P22      |                  | PCL               | specified in 4-bit units by software.                                                                                                                                                     | X         |                                                                                |                                                   |

| P23      |                  | BUZ               |                                                                                                                                                                                           |           |                                                                                |                                                   |

| P30*2    |                  | LCDCL             | Programmable 4-bit input/output port                                                                                                                                                      |           | Input                                                                          | E-B                                               |

| P31*2    | Input/           | SYNC              | (PORT3)<br>This port can be specified for input/                                                                                                                                          | v         |                                                                                |                                                   |

| P32*2    | Output           | _                 | output in bit units.<br>Internal pull-up resistors can be                                                                                                                                 | Х         |                                                                                |                                                   |

| P33*2    |                  | _                 | specified in 4-bit units by software.                                                                                                                                                     |           |                                                                                |                                                   |

| P40-43*2 | Input/<br>Output | _                 | N-ch open-drain 4-bit input/output port<br>(PORT4)<br>Internal pull-up resistors can be<br>specified in bit units. (mask option)<br>Resistive voltage is 10 V in the open-<br>drain mode. |           | High level<br>(with internal<br>pull-up<br>resistor) or<br>high imped-<br>ance | М                                                 |

| P50-53*2 | Input/<br>Output | _                 | N-ch open-drain 4-bit input/output port<br>(PORT5)<br>Internal pull-up resistors can be<br>specified in bit units. (mask option)<br>Resistive voltage is 10 V in the open-<br>drain mode. | 0         | High level<br>(with internal<br>pull-up<br>resistor) or<br>high imped-<br>ance | Μ                                                 |

\*1: Circles indicate Schmitt trigger inputs.

2: Can directly drive LED.

# 3.1 PORT PINS (2/2)

| Pin Name | Input/Output | Also Served<br>As | Function                                                                | 8-Bit I/O | When Reset | Input/<br>Output<br>Circuit<br>TYPE*1 |

|----------|--------------|-------------------|-------------------------------------------------------------------------|-----------|------------|---------------------------------------|

| P60      |              | KR0               | Programmable 4-bit input/output port                                    |           |            | (F)-A                                 |

| P61      | Input/       | KR1               | (PORT6)<br>This port can be specified for input/                        |           | Input      |                                       |

| P62      | Output       | KR2               | output in bit units.<br>Internal pull-up resistors can be               |           |            |                                       |

| P63      |              | KR3               | specified in 4-bit units by software.                                   | 0         |            |                                       |

| P70      |              | KR4               |                                                                         |           |            |                                       |

| P71      | Input/       | KR5               | 4-bit input/output port (PORT7)<br>Internal pull-up resistors can be    |           | Input      | (F)-A                                 |

| P72      | Output       | KR6               | specified in 4-bit units by software.                                   |           |            |                                       |

| P73      |              | KR7               |                                                                         |           |            |                                       |

| P80      |              |                   |                                                                         |           | Input      |                                       |

| P81      | Input/       | Input/            | 4-bit input/output port (PORT8)                                         |           |            |                                       |

| P82      | Output       | _                 | Internal pull-up resistors can be specified in 4-bit units by software. | x         |            | E-B                                   |

| P83      |              |                   |                                                                         |           |            |                                       |

| BP0      |              | S24               |                                                                         |           |            |                                       |

| BP1      | Output       | S25               |                                                                         |           |            |                                       |

| BP2      | Output       | S26               |                                                                         |           | *2         | G-C                                   |

| BP3      |              | S27               | 1-bit output port (BIT PORT)                                            | x         |            |                                       |

| BP4      |              | S28               | Shared with a segment output pin.                                       |           |            |                                       |

| BP5      | Output       | S29               |                                                                         |           |            |                                       |

| BP6      | Output       | S30               |                                                                         |           |            |                                       |

| BP7      |              | S31               |                                                                         |           |            |                                       |

\*1: Circles indicate schmidt trigger inputs.

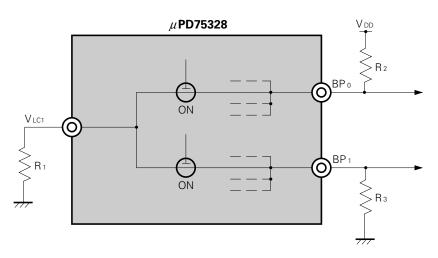

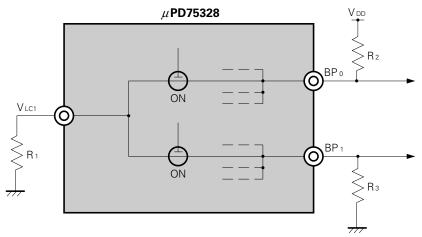

2: For BP0-7, VLc1 indicated below are selected as the input source. However, the output level is changed depending on BP0-7 and the VLc1 external circuits.

Example: Since BP0-7 are connected to each other within the  $\mu$ PD75328 as shown in the diagram below, the output level of BP0-7 depends on the sizes of R<sub>1</sub>, R<sub>2</sub> and R<sub>3</sub>.

# 3.2 NON PORT PINS

| Pin Name      | Input/Output     | Also Served<br>As | Functor                                                    | 1                                                                | When Reset | Input/<br>Output<br>Circuit<br>TYPE*1 |

|---------------|------------------|-------------------|------------------------------------------------------------|------------------------------------------------------------------|------------|---------------------------------------|

| TI0           | Input            | P13               | Timer/event counter externa                                | l event pulse Input                                              | Input      | B-C                                   |

| PTO0          | Output           | P20               | Timer/event counter output                                 |                                                                  | Input      | E-B                                   |

| PCL           | Input/<br>Output | P22               | Clock output                                               |                                                                  | Input      | E-B                                   |

| BUZ           | Input/<br>Output | P23               | Fixed frequency output (for<br>ming the system clock)      | buzzer or for trim-                                              | Input      | E-B                                   |

| SCK           | Input/<br>Output | P01               | Serial clock input/output                                  |                                                                  | Input      | (F)-A                                 |

| SO/SB0        | Input/<br>Output | P02               | Serial data output<br>Serial bus input/output              |                                                                  | Input      | (F)-В                                 |

| SI/SB1        | Input/<br>Output | P03               | Serial data input<br>Serial bus input/output               |                                                                  | Input      | <b>М</b> -с                           |

| INT4          | Input            | P00               | Edge detection vector interrorising and falling edge detec |                                                                  | Input      | B                                     |

| INT0          | laset            | P10               | Edge detection vector                                      | Clock synchronous                                                | Input      |                                       |

| INT1          | Input            | P11               | edge can be selected)                                      | interrupt input (detection<br>edge can be selected) Asynchronous |            | B-C                                   |

| INT2          | Input            | P12               | Edge detection testable<br>input (rising edge detection)   | Asynchronous                                                     | Input      | B-C                                   |

| KR0-KR3       | Input/<br>Output | P60-P63           | Parallel falling edge detection testable input/output      |                                                                  | Input      | (F-A                                  |

| KR4-KR7       | Input/<br>Output | P70-P73           | Parallel falling edge detection testable input/output      |                                                                  | Input      | (F)-A                                 |

| S12-S23       | Output           | —                 | Segment signal output                                      |                                                                  | *4         | G-A                                   |

| S24-S31       | Output           | BP0-7             | Segment signal output                                      |                                                                  | *4         | G-C                                   |

| COM0-<br>COM3 | Output           | _                 | Common signal output                                       |                                                                  | *4         | G-B                                   |

| VLC0-VLC2     | _                | _                 | LCD drive power<br>Step-down resistor network              | (mask option)                                                    | _          |                                       |

| BIAS          | Output           | _                 | External expanded driver for                               | External expanded driver for disconnect output                   |            |                                       |

| LCDCL*3       | Input/<br>Output | P30               | Externally expanded driver for clock output                |                                                                  | Input      | E-B                                   |

| SYNC*3        | Input/<br>Output | P31               | Externally expanded driver sync clock output               |                                                                  | Input      | E-B                                   |

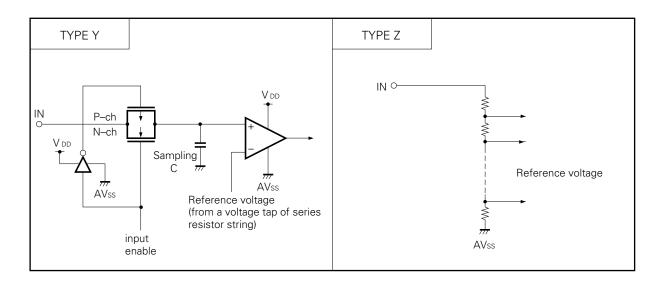

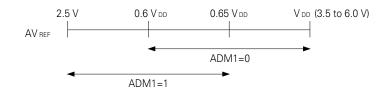

| AN0-AN5       | Input            | _                 | 6-bit analog input for A/D converter                       |                                                                  | Input      | Y                                     |

| AVREF         | Input            | _                 | A/D converter reference volt                               | age input                                                        | Input      | Z                                     |

| AVss          | _                | _                 | GND potential for A/D conve<br>input. Connected to Vss.    | erter reference voltage                                          | _          | _                                     |

#### (cont'd)

| Pin Name | Input/Output | Also Served<br>As | Function                                                                                                                                                                                                                                  | When Reset | Input/<br>Output<br>Circuit<br>TYPE*1 |

|----------|--------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------------------------------------|

| X1,X2    | _            | _                 | To connect the crystal/ceramic oscillator to<br>the main system clock generator. When<br>inputting the external clock, input the<br>external clock to pin X1, and the reverse<br>phase of the external clock to pin X2.                   | _          | Ι                                     |

| XT1, XT2 | _            | _                 | To connect the crystal oscillator to the<br>subsystem clock generator.<br>When the external clock is used, pin XT1<br>inputs the external clock. In this case, pin<br>XT2 must be left open.<br>Pin XT1 can be used as a 1-bit input pin. | _          |                                       |

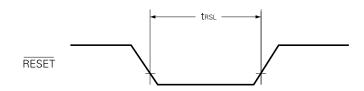

| RESET    | Input        | _                 | System reset input                                                                                                                                                                                                                        | _          | B                                     |

| NC *2    |              | _                 | No connection                                                                                                                                                                                                                             |            | _                                     |

| Vdd      |              | _                 | Positive power supply                                                                                                                                                                                                                     | _          | _                                     |

| Vss      | _            | _                 | GND                                                                                                                                                                                                                                       | _          | _                                     |

\*1: Circles indicate schmidt trigger inputs.

- 2: When sharing the printed circut board with the  $\mu$ PD75P328, the NC pin must be connected to V<sub>DD</sub>.

- 3: These pins are provided for future system expansion. At present, these pins are used only as pins P30 and P31.

- 4: For these display output, VLCX indicated below are selected as the input source.

S12 to S31: VLC1, COM0 to COM2: VLC2, COM3: VLC0

However, display output level varies depending on the particular display output and  $V_{LCX}$  external circuit.

Example: Since BP0-7 are connected to each other within the  $\mu$ PD75328 as shown in the diagram below, the output level of BP0-7 depends on the size of R<sub>1</sub>, R<sub>2</sub> and R<sub>3</sub>.

5: Step-down resistor network provided : Low level Step-down resistor network not provided : High impedance

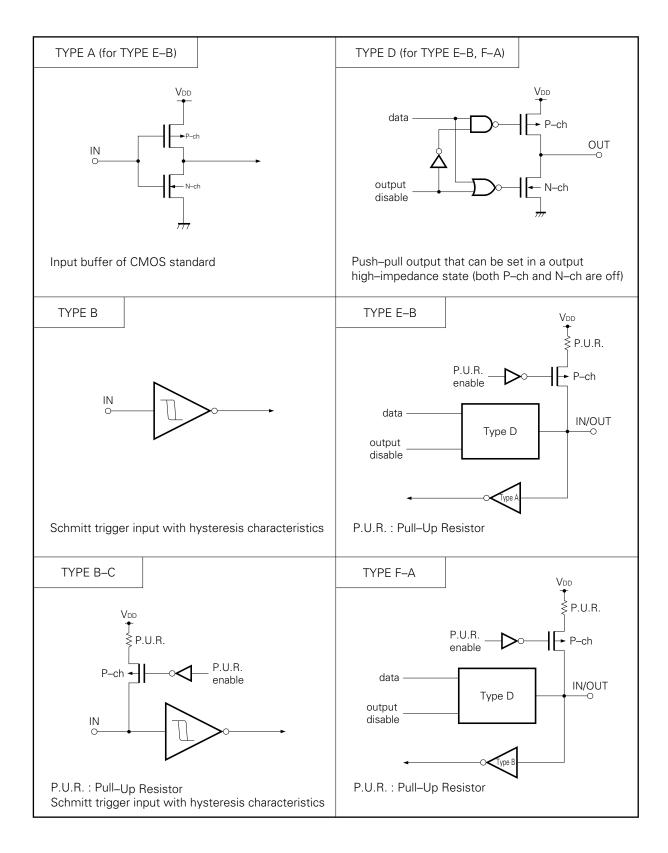

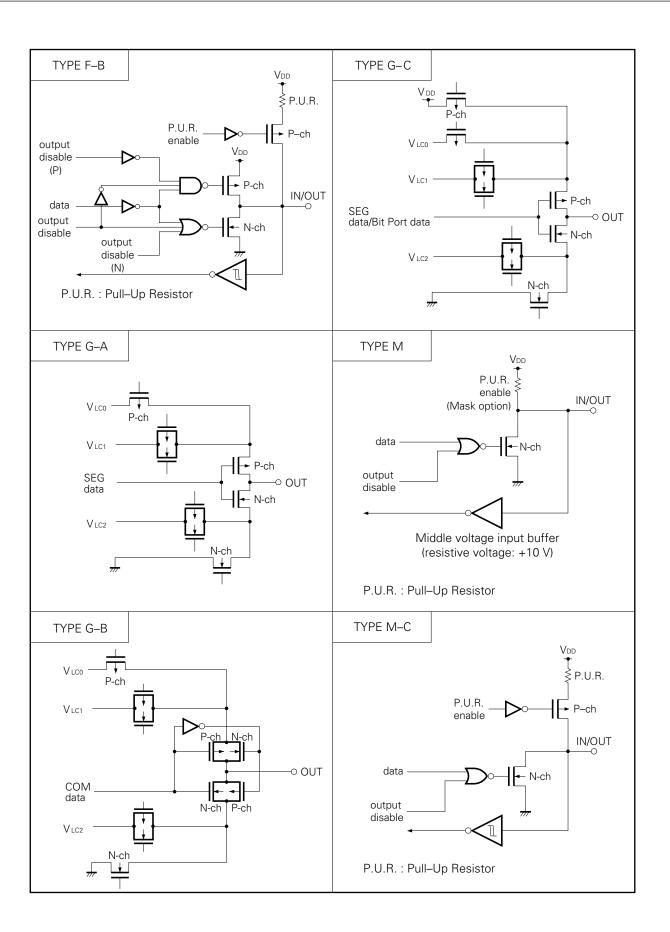

# 3.3 PIN INPUT/OUTPUT CIRCUITS

The following shows a simplified input/output circuit diagram for each pin of the  $\mu$ PD75328.

#### 3.4 RECOMMENDED PROCESSING OF UNUSED PINS

| Pin               | Recommended Connections                       |  |  |

|-------------------|-----------------------------------------------|--|--|

| P00/INT4          | Connect to Vss                                |  |  |

| P01/SCK           |                                               |  |  |

| P02/SO/SB0        | Connect to Vss or VDD                         |  |  |

| P03/SI/SB1        |                                               |  |  |

| P10/INT0-P12/INT2 | 0                                             |  |  |

| P13/TI0           | Connect to Vss                                |  |  |

| P20/PTO0          |                                               |  |  |

| P21               |                                               |  |  |

| P22/PCL           |                                               |  |  |

| P23/BUZ           |                                               |  |  |

| P30-P33           | Input : Connect to Vss or VDD                 |  |  |

| P40-P43           | Output: Open                                  |  |  |

| P50-P53           |                                               |  |  |

| P60-P63           |                                               |  |  |

| P70-P73           |                                               |  |  |

| P80-P83           |                                               |  |  |

| S12-S23           |                                               |  |  |

| S24/BP0-S31/BP7   | Open                                          |  |  |

| COM0-COM3         |                                               |  |  |

| VLC0-VLC2         | Connect to Vss                                |  |  |

| BIAS              | Connect to Vss only when All of the VLC0-VLC2 |  |  |

|                   | pins are unused, otherwise, open.             |  |  |

| XT1               | Connect to Vss or VDD                         |  |  |

| XT2               | Open                                          |  |  |

| AVREF             | Connect to Vss                                |  |  |

| AVss              | Connect to Vss                                |  |  |

| AN0-AN5           | Connect to Vss or VDD                         |  |  |

# 3.5 SELECTION OF MASK OPTION

The following mask operations are available and can be specified for each pin.

| Pin                 | Mask                                                            | Remarks                                                            |                                 |

|---------------------|-----------------------------------------------------------------|--------------------------------------------------------------------|---------------------------------|

| P40-P43,<br>P50-P53 | With pull-up resistor                                           | Without pull-up resistor                                           | Specification in bit units      |

| VLC0-VLC2<br>BIAS   | With voltage dividing<br>resistor for LCD drive<br>power source | Without voltage dividing<br>resistor for LCD drive<br>power source | Specification in 4-bit<br>units |

| XT1, XT2            | With feed back resistor<br>(when using the subsystem<br>clock)  | Without feed back resistor<br>(when using the subsystem<br>clock)  |                                 |

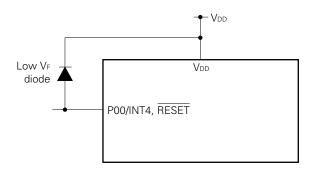

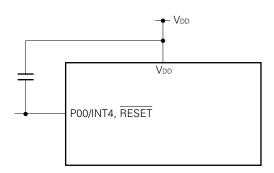

### 3.6 NOTES ON USING THE P00/INT4, AND RESET PINS

In addition to the functions described in Sections 3.1 and 3.2, an exclusive function for setting the test mode, in which the internal fuctions of the  $\mu$ PD75328 are tested, is provided to the P00/INT4 and RESET pins.

If a voltage exceeding  $V_{DD}$  is applied to either of these pins, the  $\mu$ PD75328 is put into test mode. Therefore, even when the  $\mu$ PD75328 is in normal operation, if noise exceeding the  $V_{DD}$  is input into any of these pins, the  $\mu$ PD75328 will enter the test mode, and this will cause problems for normal operation.

As an example, if the wiring to the P00/INT4 pin or the RESET pin is long, stray noise may be picked up and the above montioned problem may occur.

Therefore, all wiring to these pins must be made short enough to not pick up stray noise. If noise cannot be avoided, suppress the noise using a capacitor or diode as shown in the figure below.

Connect a diode having a low V<sub>F</sub> across P00/INT4 and RESET, and V<sub>DD</sub>.

• Connect a capacitor across P00/INT4 and  $$\overline{\sf RESET}$$  , and  $V_{\sf DD}.$

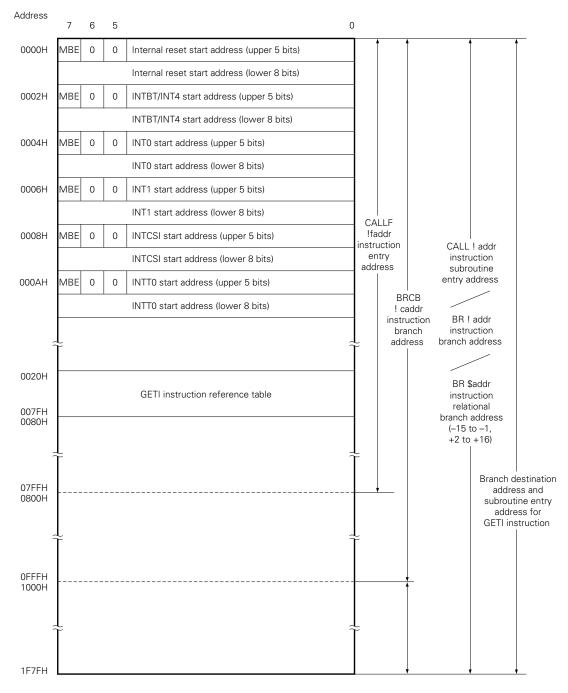

## 4. MEMORY CONFIGURATION

- Program memory (ROM) ... 8064 words  $\times$  8 bits

- 0000H, 0001H: Vector table to which address from which program is started is written after reset

- 0002H-000BH : Vector table to which address from which program is started is written after interrupt

- 0020H-007FH : Table area referenced by GETI instruction

- Data memory

- + Data area .... 512 words  $\times$  4 bits (000H–1FFH)

- Peripheral hardware area .... 128 words × 4 bits (F80H–FFFH)

Fig. 4-1 Program Memory Map

| •                                      |       | General-purpose<br>register<br>area | 000H<br>007H | (8 × 4)              |           |

|----------------------------------------|-------|-------------------------------------|--------------|----------------------|-----------|

| Data area<br>(Static RAM<br>(512 x 4)) | Stack | < area                              | 008H         | 256 × 4<br>(248 × 4) | Bank 0    |

|                                        |       | •                                   | 0FFH         |                      |           |

|                                        |       |                                     | 100H         | 256 × 4<br>(236 × 4) |           |

|                                        |       |                                     | 1EBH         |                      | Bank 1    |

|                                        |       | Display<br>data<br>memory           | 1ECH<br>1FFH | (20 × 4)             | <b>,</b>  |

|                                        |       |                                     |              | Not provided         | <br> <br> |

|                                        |       |                                     | F80H         |                      |           |

| Peripheral hardware                    | area  |                                     |              | 128 x 4              | Bank 15   |

|                                        |       |                                     | FFFH         |                      |           |

Fig. 4-2 Data Memory Map

## 5. PERIPHERAL HARDWARE FUNCTIONS

#### 5.1 PORTS

I/O ports are classified into the following 4 kinds:

- CMOS input (PORT0, 1) : 8

- CMOS input/output (PORT2, 3, 6, 7, and 8) : 20

- CMOS output (BP0-BP7) : 8

- N-ch open-drain input/output (PORT4, 5) : 8

```

Total

```

| Table | 5-1 | Port | Function |

|-------|-----|------|----------|

|-------|-----|------|----------|

: 44

| Port Name          | Function                                         | Operation and Feature                                                                                                         | Remarks                                                                     |

|--------------------|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| PORT0              |                                                  | Can be always read or tested regardless of                                                                                    | Multiplexed with INT4, SCK, SO/SB0, and SI/SB1                              |

| PORT1              | 4-bit input                                      | operation mode of multiplexed pin.                                                                                            | Multiplexed with INT0-<br>INT2 and TI0                                      |

| PORT2              |                                                  | Can be set in input or output mode in 4-bit units.                                                                            | Multiplexed with PTO0, PCL, and BUZ                                         |

| PORT7              |                                                  | Ports 6 and 7 are used in pairs to input/output data in 8-bit units.                                                          | Multiplexed with KR4-KR7                                                    |

| PORT8              | 4-bit Input/Output                               |                                                                                                                               | _                                                                           |

| PORT3              |                                                  | Can be set in input or output mode in 1-bit units.                                                                            | Multiplexed with LCDCL and SYNC                                             |

| PORT6              |                                                  |                                                                                                                               | Multiplexed with KR0-KR3                                                    |

| PORT4 *<br>PORT5 * | 4-bit Input/Output<br>(N-ch open-drain,<br>10 V) | Can be set in input or output mode in 4-bit units.<br>Ports 4 and 5 are used in pairs to input/output data<br>in 8-bit units. | Can be connected to a pull-up resistor in 1-bit units by using mask option. |

| BP0-BP7            | 1-bit output                                     | Output data in 1-bit units. Can be used as LCD drive segment output pins S24-S31 through software.                            | _                                                                           |

\*: Can directly drive LED.

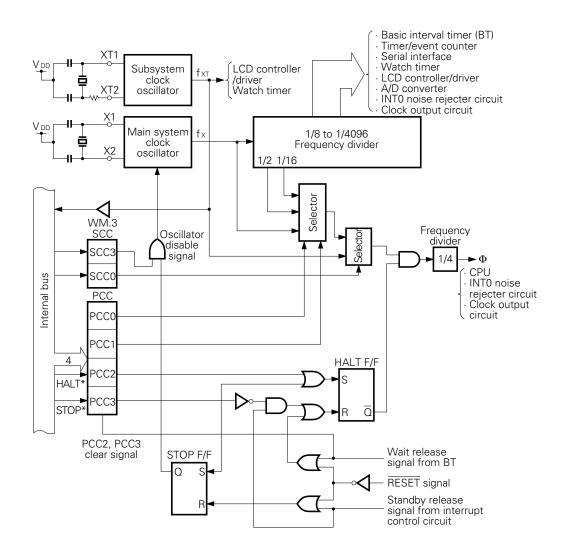

# 5.2 CLOCK GENERATOR CIRCUIT

The operation of the clock generator circuit is determined by the processor clock control regiser (PPC) and system clock control register (SCC).

This circuit can generate two types of clocks: main system clock and subsystem clock. In addition, it can also change the instruction execution time.

- 0.95 μs, 1.91 μs, 15.3 μs (main system clock: 4.19 MHz)

- 122 μs (subsystem clock: 32.768 kHz)

\*: instruction execution.

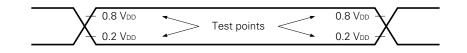

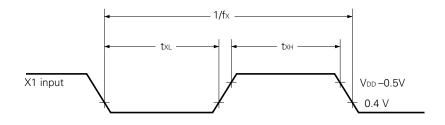

**Remarks** 1: fx = Main system clock frequency

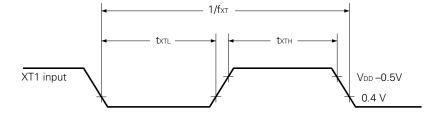

- 2: fxT = Subsystem clock frequency

- 3:  $\Phi$  = CPU clock

- 4: PCC: Processor clock control register

- 5: SCC: System clock control register

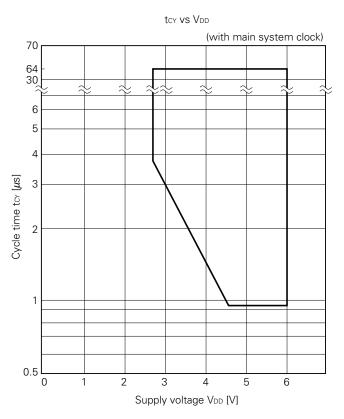

- 6: One clock cysle ( $t_{CY}$ ) of  $\Phi$  is one machine cycle of an instruction. For  $t_{CY}$ , refer to AC characteristics in 10. ELECTRICAL SPECIFICATIONS.

### Fig. 5-1 Clock Generator Block Diagram

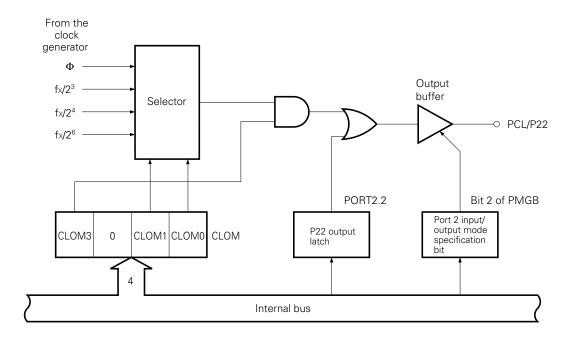

### 5.3 CLOCK OUTPUT CIRCUIT

The clock output circuit outputs clock pulse from the P22/PCL pin. This clock pulse is used for the remote control output, peripheral LSIs, etc.

## Fig. 5-2 Clock Output Circuit Configuration

*Remarks:* A measures to prevent outputting narrow width pulse when selecting clock output enable/disable is taken.

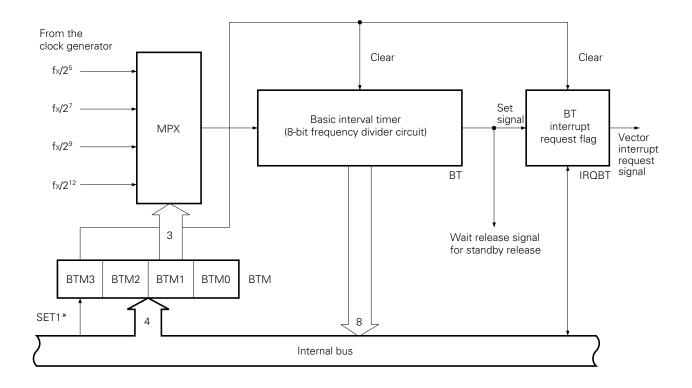

#### 5.4 BASIC INTERVAL TIMER

The  $\mu$ PD75328 is provided with the 8-bit basic interval timer. The basic interval timer has these functions:

- Interval timer operation which generates a reference time interrupt

- Watchdog timer application which detects a program runaway

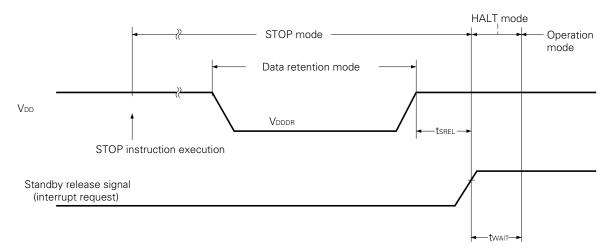

- Selects the wait time for releasing the standby mode and counts the wait time

- Reads out the count value

Remarks : \*: Instruction execution

#### Fig. 5-3 Basic Interval Timer Configuration

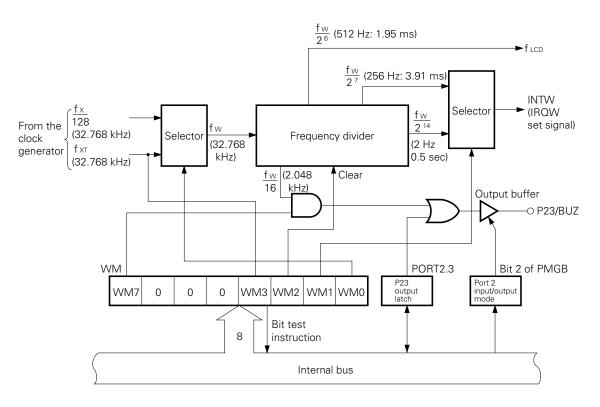

#### 5.5 WATCH TIMER

The  $\mu$ PD75328 has a built-in 1-ch watch timer. The watch timer is configured as shown in Fig. 5-4.

- Sets the test flag (IRQW) with 0.5 sec interval. The standby mode can be released by IRQW.

- 0.5 second interval can be generated either from the main system clock or subsystem clock.

- Time interval can be advanced to 128 times faster (3.91 ms) by setting the fast mode. This is convenient for program debugging, test, etc.

- Fixed frequency (2.048 kHz) can be output to the P23/BUZ pin. This can be used for beep and system clock frequency trimming.

- The frequency divider circuit can be cleared so that zero second watch start is possible.

( ) is for fx = 4.194304 MHz, fxT = 32.768 kHz.

#### Fig. 5-4 Watch Timer Block Diagram

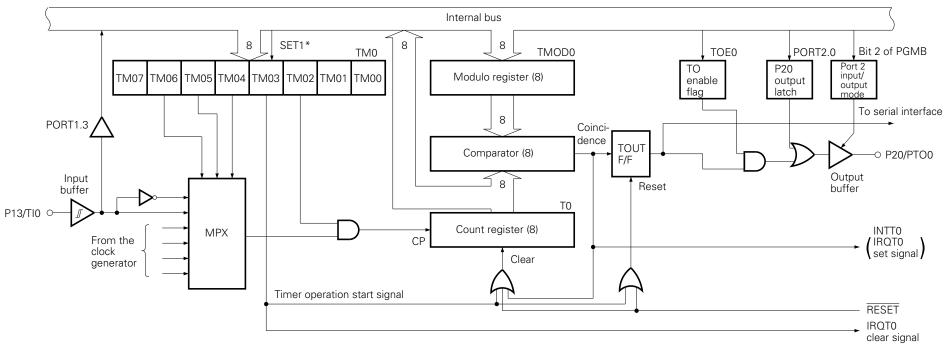

#### 5.6 TIMER/EVENT COUNTER

The  $\mu$ PD75328 has a built-in 1-ch timer/event counter. The timer/even counter has these functions:

- Programmable interval timer operation

- Outputs square-wave signal of an arbitrary frequency to the PTO0 pin.

- Event counter operation

- Divides the TIO pin input in N and outputs to the PTOO pin (frequency divider operation).

- Supplies serial shift clock to the serial interface circuit.

- Count condition read out function

\*:Instruction execution

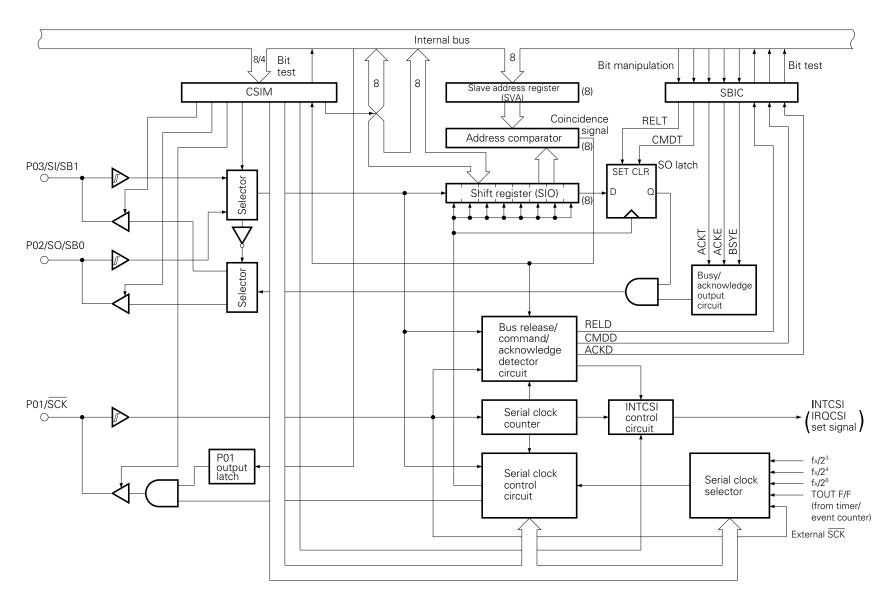

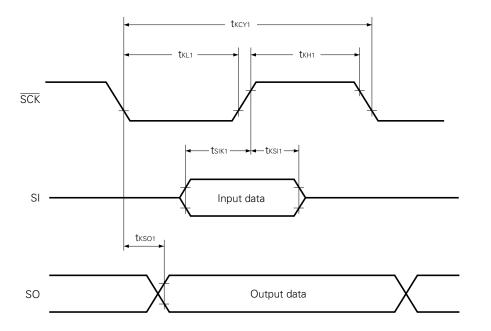

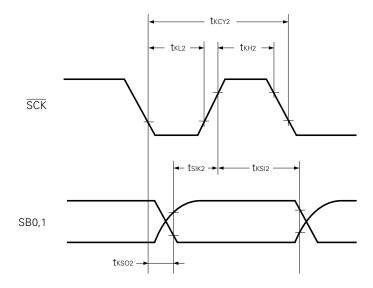

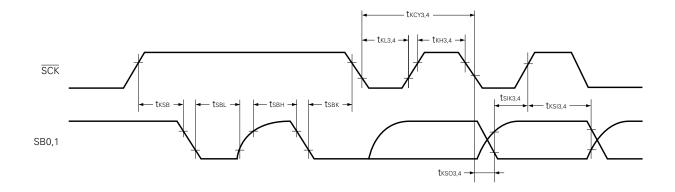

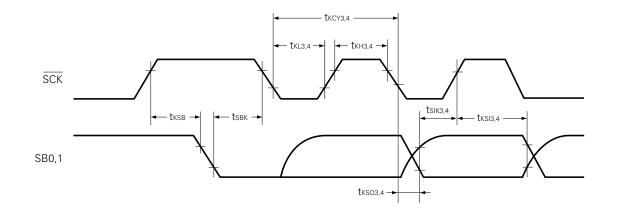

#### 5.7 SERIAL INTERFACE

The  $\mu$ PD75328 is equipped with an 8-bit clocked serial interface that operates in the following four modes:

- Operation stop mode

- Three-line serial I/O mode

- Two-line serial I/O mode

- SBI mode (serial bus interface mode)

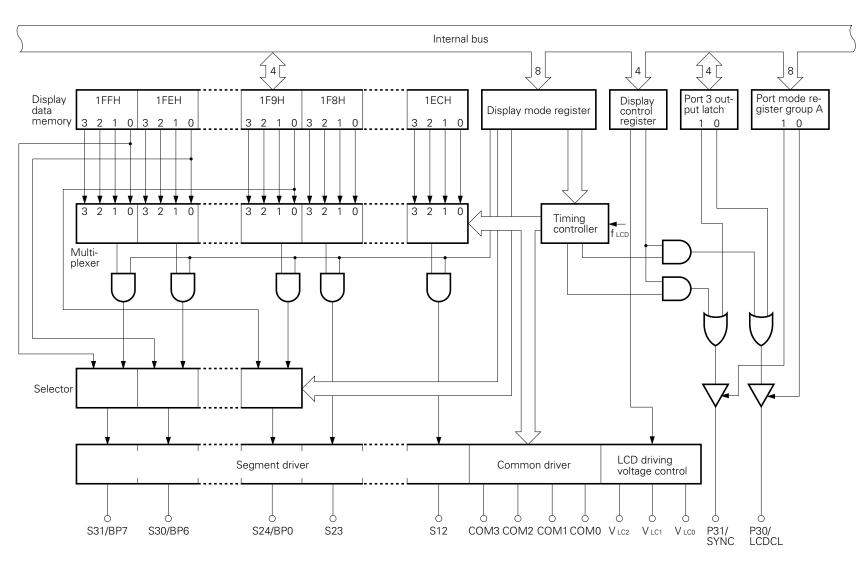

## 5.8 LCD CONTROLLER/DRIVER

The  $\mu$ PD75328 is provided with a display controller that generates segment and common signals and a segment driver and a common driver that can directly drive an LCD panel. These LCD controller and drivers have the following functions:

- Generate segment and common signals by automatically reading the display data memory by means of DMA

- Five display modes selectable

- Static

- 1/2 duty (divided by 2), 1/2 bias

- 1/3 duty (divided by 3), 1/2 bias

- 1/3 duty (divided by 3), 1/3 bias

- 1/4 duty (divided by 4), 1/3 bias

- Four types of frame frequencies selectable in each display mode

- Up to 20 segment signals (S12-S31) and four common signals (COM0-COM3) can be output.

- Four segment signal output pins (S24-S27, S28-S31) can be used as an output port (BP0-BP3, BP4-BP7).

- Dividing resistor for LCD driving power source can be provided (by mask option).

- All bias modes and LCD drive voltages can be used.

- Current flowing to dividing resistor can be cut when display is off.

- Display data memory not used for display can be used as ordinary data memory.

- Can also operate on subsystem clock.

Fig. 5-7 LCD Controller/Driver Block Diagram

27

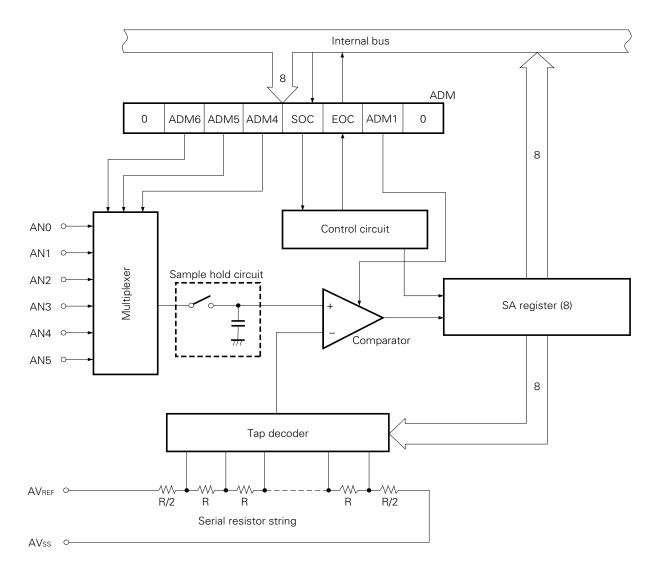

# 5.9 A/D CONVERTER

The  $\mu$ PD75328 is provided with an 8-bit resolution analog-to-digital (A/D) converter with six channels of analog inputs (AN0-AN5).

This A/D converter is of a successive approximation type.

Fig. 5-8 Block Diagram of A/D Converter

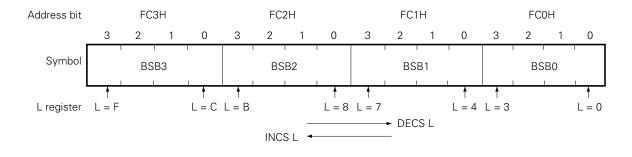

#### 5.10 BIT SEQUENTIAL BUFFER .... 16 BITS

The bit sequential buffer is a data memory specifically provided for bit manipulation. With this buffer, addresses and bit specifications can be sequentially up-dated in bit manipulation operation. Therefore, this buffer is very useful for processing long data in bit units.

#### Fig. 5-9 Bit Sequential Buffer Format

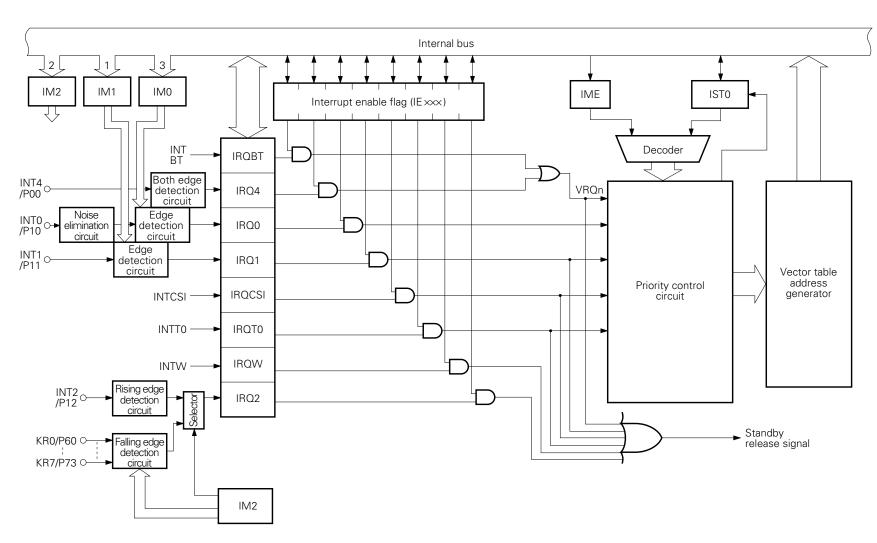

#### 6. INTERRUPT FUNCTIONS

The  $\mu$ PD75328 has 6 different interrupt sources and multiplexed interrupt with priority order. In addition to that, the  $\mu$ PD75328 is also provided with two types of test sources, of which INT2 has two types of edge detection testable inputs.

The interrupt control circuit of the  $\mu$ PD75328 has these functions:

- Hardware controlled vector interrupt function which can control whether or not to accept an interrupt by using the interrupt flag (IExxx) and interrupt master enable flag (IME).

- The interrupt start address can be arbitrarily set.

- Interrupt request flag (IRQxxx) test function (an interrupt generation can be confirmed by means of software).

- Standby mode release (Interrupts to be released can be selected by the interrupt enable flag).

µ**PD75328**

# 7. STANDBY FUNCTIONS

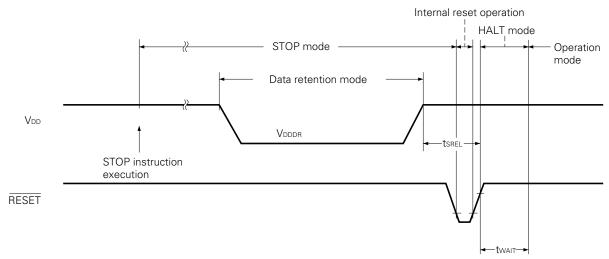

The  $\mu$ PD75328 has two different standby modes (STOP mode and HALT mode) to reduce the power consumption while waiting for program execution.

| ltem                | Mode                    | STOP Mode                                                                                                                     | HALT Mode                                                                                                                     |

|---------------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| Setting In          | struction               | STOP instrtuction                                                                                                             | HALT instruction                                                                                                              |

| System C            | lock for Setting        | Can be set only when operating on the main system clock                                                                       | Can be set either with the main system clock or the subsystem clock                                                           |

| Operation<br>Status | Clock Generator         | Only the main system clock stops its operation.                                                                               | Only the CPU clock $\Phi$ stops its operation. (oscillation continues)                                                        |

|                     | Basic Interval<br>Timer | No operation                                                                                                                  | Can operate only when main system<br>clock oscillates (Sets IRQBT at<br>reference time interval)                              |

|                     | Serial Interface        | Can operate only when the external SCK input is selected for the serial clock                                                 | Can operate only when main system<br>clock oscillates, or when external<br>SCK input is selected as serial clock              |

|                     | Timer/Event<br>Counter  | Can operate only when the TI0 pin input is selected for the count clock                                                       | Can operate only when main system<br>clock oscillates, or when Tl0 pin<br>input is selected as count clock                    |

|                     | Watch Timer             | Can operate when fxr is selected as the count clock                                                                           | Can operate                                                                                                                   |

|                     | LCD controller          | Can operate only when fxT is selected as LCDCL                                                                                | Can operate                                                                                                                   |

|                     | A/D Convertor           | No operation                                                                                                                  | Can operate only when the main system clock is operating.                                                                     |

|                     | External Interrupt      | INT1, INT2, and INT4 can operate.<br>Only INT0 can not operate.                                                               |                                                                                                                               |

|                     | CPU                     | No operation                                                                                                                  |                                                                                                                               |

| Release Signal      |                         | An interrupt request signal from a hardware whose operation is enabled by the interrupt enable flag or the RESET signal input | An interrupt request signal from a hardware whose operation is enabled by the interrupt enable flag or the RESET signal input |

# Table 7-1 Each Status in Standby Mode

# 8. RESET FUNCTION

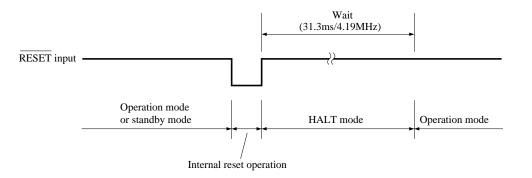

When the  $\overrightarrow{\text{RESET}}$  signal is input, the  $\mu$ PD75328 is reset and each hardware is initialized as indicated in Table 8-1. Fig. 8-1 shows the reset operation timing.

Fig. 8-1 Reset Operation by RESET Input

| Table 8-1 | Status of Each | Hardware            | after Reset (1/2) |  |

|-----------|----------------|---------------------|-------------------|--|

|           |                | i i i a i a i a i a |                   |  |

| Hardware |                                                                                                                       | Hardware                   | <b>RESET</b> Input in Standby Mode                                                                                                                         | <b>RESET</b> Input during Operation                                                |

|----------|-----------------------------------------------------------------------------------------------------------------------|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| Progra   | of address 0000H of the program of address 0000H of the program memory are set to PC12-8, and memory are set to PC12- |                            | The contents of the lower 5 bits<br>of address 0000H of the program<br>memory are set to PC12-8, and<br>the contents of address 0001H<br>are set to PC7-0. |                                                                                    |

| PSW      | Carry I                                                                                                               | Flag (CY)                  | Retained                                                                                                                                                   | Undefined                                                                          |

|          | Skip F                                                                                                                | lag (SK0-2)                | 0                                                                                                                                                          | 0                                                                                  |

|          | Interru                                                                                                               | pt Status Flag (IST0)      | 0                                                                                                                                                          | 0                                                                                  |

|          | Bank Enable Flag (MBE)                                                                                                |                            | The contents of bit 7 of address<br>0000H of the program memory<br>are set to MBE.                                                                         | The contents of bit 7 of address<br>0000H of the program memory<br>are set to MBE. |

| Stack    | Pointer                                                                                                               | (SP)                       | Undefined                                                                                                                                                  | Undefined                                                                          |

| Data N   | Memory                                                                                                                | (RAM)                      | Retained *1                                                                                                                                                | Undefined                                                                          |

|          | al-Purpo<br>H, L, D,                                                                                                  | se Register<br>E, B, C)    | Retained                                                                                                                                                   | Undefined                                                                          |

| Bank S   | Selectior                                                                                                             | n Register (MBS)           | 0                                                                                                                                                          | 0                                                                                  |

|          |                                                                                                                       | Counter (BT)               | Undefined                                                                                                                                                  | Undefined                                                                          |

| Timer    |                                                                                                                       | Mode Register (BTM)        | 0                                                                                                                                                          | 0                                                                                  |

|          | /Event                                                                                                                | Counter (T0)               | 0                                                                                                                                                          | 0                                                                                  |

| Counter  |                                                                                                                       | Module Register<br>(TMOD0) | FFH                                                                                                                                                        | FFH                                                                                |

|          |                                                                                                                       | Mode Register (TM0)        | 0                                                                                                                                                          | 0                                                                                  |

|          |                                                                                                                       | TOE0, TOUT F/F             | 0, 0                                                                                                                                                       | 0, 0                                                                               |

| Watch    | Timer                                                                                                                 | Mode Register (WM)         | 0                                                                                                                                                          | 0                                                                                  |

|                         | Hardware                                                               | RESET Input in Standby Mode                                                                                      | RESET Input during Operation |

|-------------------------|------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|------------------------------|

| Serial                  | Shift Register (SIO)                                                   | Retained                                                                                                         | Undefined                    |

| Interface               | Operation Mode<br>Register (CSIM)                                      | 0                                                                                                                | 0                            |

|                         | SBI Control Register<br>(SBIC)                                         | 0                                                                                                                | 0                            |

|                         | Slave Address Register<br>(SVA)                                        | Retained                                                                                                         | Undefined                    |

| Clock<br>Generator,     | Processor Clock Control<br>Register (PCC)                              | 0                                                                                                                | 0                            |

| Clock Output<br>Circuit | System Clock Control<br>Register (SCC)                                 | 0                                                                                                                | 0                            |

|                         | Clock Output Mode<br>Register (CLOM)                                   | 0                                                                                                                | 0                            |

| LCD<br>Controller       | Display Mode Register<br>(LCMD)                                        | 0                                                                                                                | 0                            |

|                         | Display Control<br>Register (LCDC)                                     | 0                                                                                                                | 0                            |

| A/D Converter           | Mode Regiseter (ADM),<br>EOC                                           | 04H (EOC = 1)                                                                                                    | 04H (EOC = 1)                |

|                         | SA Register                                                            | 7FH                                                                                                              | 7FH                          |

| Interrupt<br>Function   | Interrupt Request Flag<br>(IRQxxx)                                     | Reset (0)                                                                                                        | Reset (0)                    |

|                         | Interrupt Enable Flag<br>(IExxx)                                       | 0                                                                                                                | 0                            |

|                         | Interrupt Master Enable<br>Flag (IME)                                  | 0                                                                                                                | 0                            |

|                         | INT0, INT1, INT2 Mode<br>Registers (IM0, 1, 2)                         | 0, 0, 0                                                                                                          | 0, 0, 0                      |

| Digital Port            | Output Buffer                                                          | Off                                                                                                              | Off                          |

|                         | Output Latch                                                           | Clear (0)                                                                                                        | Clear (0)                    |

|                         | Input/Output Mode<br>Register (PMGA, B, C)                             | 0                                                                                                                | 0                            |

|                         | Pull-Up Resistor<br>Specification Register<br>(POGA, B)                | 0                                                                                                                | 0                            |

| Pin States              | P00-P03, P10-P13,<br>P20-P23, P30-P33,<br>P60-P63, P70-P73,<br>P80-P83 | Input                                                                                                            | Input                        |

|                         | P40-P43, P50-P53                                                       | <ul> <li>Internal pull-up resistors</li> <li> High level</li> <li>Open drain</li> <li> High impedance</li> </ul> | Same as at left              |

|                         | S12-S23,<br>COM0-COM3                                                  | *2                                                                                                               | *2                           |

|                         | BIAS                                                                   | <ul> <li>Internal step-down resistors</li> <li> Low level</li> <li>External step-down resistors</li> </ul>       | Same as at left              |

|                         |                                                                        | High impedance                                                                                                   |                              |